Основные понятия и характеристики архитектуры микропроцессоров. Типовая структура ЭВМ. Современная электронная цифровая вычислительная техника широко применяется в народном хозяйстве. В настоящее время создано четыре поколения ЭВМ с улучшающимися технико-

Эта глава посвящена архитектурным особенностям микропроцессоров. В ней приведены общие сведения о микропроцессорах, рассматриваются принципы структурно - функциональной организации) типы данных, регистровая память, спо-собы адресации и система команд микропроцессоров. Излагаемый материал ил-люстрируется на простейших 8- и 16-разрядных процессорах.

Основные понятия

Микропроцессор — это программно-управляемое устройство в виде интегральной микросхемы (БИС или СБИС), предназначенное для обработки цифровой информации. Поскольку все современные микро-процессоры имеют интегральное исполнение, синонимом микропроцессора стал термин процессор.

Микроконтроллер — это специализированный процессор, предназначен-ный для реализации функций управления (control— управление).

{xtypo_quote}Цифровой сигнальный процессор(Digital Signal Processor — DSP) — это специа-лизированный процессор, предназначенный для обработки цифровых сигналов. {/xtypo_quote}

Микропроцессорная система представляет собой функционально законченное изделие, состоящее из нескольких цифровых устройств, включая процессор. Это понятие объединяет широкий набор законченных изделий, начиная с микроконтроллеров, выполненных на интегральных микросхемах, и кон-чая компьютерными системами, представляющими собой набор отдельных конст-руктивно оформленных устройств (системный блок, клавиатура, монитор и др.). В дальнейшем рассматриваются простейшие (однокристальные) микропроцес-сорные системы, содержащие помимо процессора основную память и устройства ввода/вывода. Такие микропроцессорные системы можно отнести к классу микро-процессоров.

Под организацией процессора понимают совокупность его узлов (устройств, блоков, модулей), связи между узлами и их функциональные характе-ристики. Организация определяет аппаратную организацию процессора, т. е. состав и взаимодействие его аппаратных средств. Выделяют два уровня организации:

● физическую организацию в виде принципиальной схемы;

● логическую организацию в виде структурно-функциональной схемы.

В дальнейшем рассматривается организация микропроцессоров на логиче-ском уровне, или структурно-функциональная организация процессоров.

Под архитектурой процессора будем понимать совокупность его программно-аппаратных средств, обеспечивающих обработку цифровой инфор-мации (выполнение программы), т. е. совокупность всех средств, доступных про-грамме (или пользователю). Это более общее понятие по сравнению с понятием организация включает в себя набор программно-доступных регистров и операци-онных устройств, систему основных команд и способов адресации, объем и орга-низацию адресуемой памяти, виды и способы обработки данных (обмен, преры-вания, примой доступ к памяти и др.).

{xtypo_quote}Например, современные 32-разрядные процессоры х86 с архитектурой IA-32 (Intel Architecture — 2 bit) имеют стандарт-ный набор регистров, общую систему основных команд, одинаковые способы организации и адресации памяти, защиты памяти и обслуживания прерываний. Отметим, что понятие архитектуры в большей степени характеризует свойства системы, чем устройства. {/xtypo_quote}

Основные виды архитектур

По форматам используемых команд (инструкций) можно выделить:

● CISC-архитектуру, которая относится к процессорам (компьютерам) с полным набором команд (Complete Instruction Set Computer— CISC). Она реализова-на во многих типах микропроцессоров (например Pentium), выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации.

Система команд процессоров с CISC-архитектурой может содержать не-сколько сотен команд разного формата (от 1 до 15 байт), или степени слож-ности, и использовать более 10 различных способов адресации, что позволя-ет программисту реализовать наиболее эффективные алгоритмы решения различных задач.

Развитие традиционных CISC

Архитектур микропроцессоров по пути рас-ширения функциональных возможностей и снижения затрат на программиро-вание привело к увеличению числа команд в наборе и числа микрокоманд в команде. Следствием этого явилось усложнение интегральных схем и сни-жение быстродействия выполнения программ. Один из возможных путей уст-ранения указанных недостатков состоит в использовании сокращенного набо-ра команд, организация которого подчинена увеличению скоростей их выпол-нения;

● RISC-архитектуру, которая относится к процессорам (компьютерам) с сокра-щенным набором команд (Reduced instruction Set Computer — RISC). Появле-ние RISC -архитектуры продиктовано тем, что многие CISC -команды и спо-собы адресации используются достаточно редко. Основная особенность RISC-архитектуры проявляется в том, что система команд состоит из неболь-шого количества часто используемых команд одинакового формата, которые могут быть выполнены за один командный цикл (такт) центрального процес-сора. Более сложные, редко используемые команды реализуются на про-граммном уровне. Однако за счет значительного повышения скорости испол-нения команд средняя производительность RISC-процессоров может оказать-ся выше, чем у процессоров с CISC-архитектурой.

{xtypo_quote}Большинство команд RISC -процессоров связано с операцией регистр-регистр. Для обращения к памяти оставлены наиболее простые с точки зре-ния временных затрат операции загрузки в регистры и записи в память. {/xtypo_quote}

Современные RISC -процессоры реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта, и используют небольшое число наи-более простых способов адресации (регистровую, индексную и некоторые другие).

Для сокращения количества обращений к внешней оперативной памяти RISC -процессоры содержат десятки-сотни регистров общего назначения (РОН), тогда как в CISC

-процессорах

всего 8-16 регистров. Обращение к внешней памяти в RISC-процессорах используется только в операциях за-грузки данных в РОН или пересылки результатов из РОН в память. За счет со-кращения аппаратных средств, необходимых для декодирования и выполне-ния сложных команд, достигается существенное упрощение интегральных схем RISC-процессоров и снижение их стоимости. Кроме того, значительно повышается производительность. Благодаря указанным достоинствам во многих современных

CI SC -процессорах (последние модели Pentium и К7) ис-пользуется RISC-ядро. При этом сложные CI SC-команды предварительно преобразуются в последовательность простых RISC-операций и быстро вы-полняются RISC-ядром;

● VLIW-архитектуру, которая относится к микропроцессорам с использованием очень длинных команд (Very Large Instruction Word— VLIW). Отдельные поля команды содержат коды, обеспечивающие выполнение различных операций. Одна VLIW -команда может выполнить сразу несколько операций одновремен-но в различных узлах микропроцессора. Формирование «длинных» VLIW - koманд производит соответствующий компилятор при трансляции программ, написанных на языке высокого уровня.

{xtypo_quote}VLIW -архитектура реализована в неко-торых типах современных микропроцессоров и является весьма перспектив-ной для создания нового поколения сверхвысокопроизводительных процес-соров. {/xtypo_quote}

По способу организации выборки команд и данных различа-ют два вида архитектур:

● принстонская архитектура, или архитектура фон-Неймана, особенностью которой является (рис. 2.1.1) использование:

Общей основной (оперативной) памяти для хранения программ и данных, что позволяет оперативно и эффективно перераспределять ее объем в за-висимости от решаемых задач в каждом конкретном случае применении микропроцессора;

Общей шины, по которой в процессор поступают команды и данные, а в опе-ративную память записываются результаты, что значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Чтобы отделить команду от данных, первым из памяти всегда поступает код выполняемой операции, а затем следуют данные. По умолчанию код операции загружается в регистр команд, а дан-ные — в блок регистров (рис. 2.1.1). Из-за ограниченного числа внешних выводов общая шина обычно работает в режиме временного мультиплек-сирования, т. е. противоположные направления обмена данными между микропроцессором, памятью или другими внешними устройствами разде-лены во времени.

Недостаток принстонской архитектуры

Использование общей шины для пе-редачи команд и данных ограничивает производительность цифровой системы;

● гарвардская архитектура (создатель Говард Айкен), особенностью которой является физическое разделение памяти команд (программ) и памяти данных (рис. 2.1.2). Это обстоятельство вызвано постоянно возрастающими требова-ниями к производительности микропроцессорных систем. Память команд и память данных соединяются с процессором отдельными шинами. Благодаря разделению потоков команд и данных, а также совмещению операций их вы-борки (и записи результатов обработки) обеспечивается более высокая про-изводительность, чем при использовании принстонской архитектуры.

Недостатки гарвардской архитектуры

Усложнение конструкции из-за ис-пользования отдельных шин для команд и данных; фиксированный объем па-мяти для команд и данных; увеличение общего объема памяти из-за невоз-можности ее оптимального перераспределения между командами и данными. Гарвардская архитектура получила широкое применение в микроконтрол-лерах — специализированных микропроцессорах для управления различными объектами, а также во внутренней структуре современных высокопроизводи-тельных микропроцессоров в кэш-памяти с раздельным хранением команд и данных.

В то же время во внешней структуре большинства микропроцессор-ных систем реализуются принципы принстонской архитектуры.

Отметим, что архитектура микропроцессора тесно связана с его структурой. Реализация тех или иных архитектурных особенностей требует введении в струк-туру микропроцессора соответствующих устройств и обеспечения механизмов их совместного функционирования.

- ВВЕДЕНИЕ

- 1. Общая характеристика архитектуры процессора

- 1.1 Базовая структура микропроцессорной системы

- 1.2 Понятие архитектуры микропроцессора

- 1.3 Обзор существующих типов архитектур микропроцессоров

- 2. Устройство управления

- 3. Особенности программного и микропрограммного управления

- 4. Режимы адресации

- Заключение

- Список используемой литературы

- ВВЕДЕНИЕ

- Процесс взаимодействия человека с ЭВМ насчитывает уже более 40лет. До недавнего времени в этом процессе могли участвовать только специалисты - инженеры, математики - программисты, операторы. В последние годы произошли кардинальные изменения в области вычислительной техники. Благодаря разработке и внедрению микропроцессоров в структуру ЭВМ появились малогабаритные, удобные для пользователя персональные компьютеры. Ситуация изменилась, в роли пользователя может быть не только специалист по вычислительной технике, но и любой человек, будь то школьник или домохозяйка, врач или учитель, рабочий или инженер. Часто это явление называют феноменом персонального компьютера. В настоящее время мировой парк персональных компьютеров превышает 20 млн.

- Почему возник этот феномен? Ответ на этот вопрос можно найти, если четко сформулировать, что такое персональный компьютер и каковы его основные признаки. Надо правильно воспринимать само определение " персональный", оно не означает принадлежность компьютера человеку на правах личной собственности. Определение "персональный" возникло потому, что человек получил возможность общаться с ЭВМ без посредничества профессионала-программиста, самостоятельно, персонально. При этом не обязательно знать специальный язык ЭВМ. Существующие в компьютере программные средства обеспечат благоприятную " дружественную" форму диалога пользователя и ЭВМ.

- В настоящее время одними из самых популярных компьютеров стали модель IBM PC и ее модернизированный вариант IBM PC XT, который по архитектуре, программному обеспечению, внешнему оформлению считается базовой моделью персонального компьютера.

- Основой персонального компьютера является системный блок. Он организует работу, обрабатывает информацию, производит расчеты, обеспечивает связь человека и ЭВМ. Пользователь не обязан досконально разбираться в том, как работает системный блок. Это удел специалистов. Но он должен знать, из каких функциональных блоков состоит компьютер. Мы не имеем четкого представления о принципе действия внутренних функциональных блоков окружающих нас предметов - холодильника, газовой плиты, стиральной машины, автомобиля, но должны знать, что заложено в основу работы этих устройств, каковы возможности составляющих их блоков.

Архитектура микропроцессора - это совокупность сведений о составе его компонентов, организации обработки в нем информации и обмена информацией с внешними устройствами ЭВМ, а также о функциональных возможностях микропроцессора, выполняющего команды программы.

Структура микропроцессора - это сведения только о составе его компонентов, соединениях между ними, обеспечивающих их взаимодействие. Таким образом, архитектура является более общим понятием, включающим в себя кроме структуры еще и представление о функциональном взаимодействии компонентов этой структуры между собой и с внешней средой.

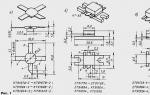

Основой любого МП (рис.14) является арифметико-логическое устройство АЛУ, выполняющее обработку информации - арифметические и логические действия над исходными данными и соответствии с командами. Сами данные (исходные, промежуточные и конечный результат) находятся в регистрах данных РД, а команды - в регистре команд РК. Управление всеми процессами по вводу и выводу информации, взаимодействию между АЛУ, РД и РК осуществляет многофункциональное устройство управления УУ. Данные, команды и управляющие сигналы передаются по внутренней шине ВШ.

Рис.14 Типовая структурная схема МП

Каждый микропроцессор имеет свой внутренний язык, называемый множеством микрокоманд или составом команд – это набор команд, которые понимает и может выполнять данный микропроцессор.

В течение каждого цикла команды ЦП выполняет много управляющих функций:

1) помещает адрес команды в адресную шину памяти;

2) получает команду из шины ввода данных и дешифрирует ее;

3) выбирает адреса и данные, содержащиеся в команде; адреса и данные могут находиться в памяти или в регистрах;

4) выполняет операцию, определенную в коде команды. Операцией может быть арифметическая или логическая функция, передача данных или функция управления;

5) следит за управляющими сигналами, такими как прерывание, и реагирует соответствующим образом;

6) генерирует сигналы состояния, управления и времени, которые необходимы для нормальной работы УВВ и памяти.

Таким образом, ЦП является «мозгом», определяющим действия ЭВМ.

Рис.15 Цикл команды процессора

По характеру исполняемого кода и организации устройства управления выделяется несколько типов архитектур:

- Процессор со сложным набором инструкций , англ. CISC - Complex Instruction Set Computer . Эту архитектуру характеризует большое количество сложных инструкций, и как следствие сложное устройство управления. В ранних вариантах CISC-процессоров и процессоров для встроенных приложений характерны большие времена исполнения инструкций (от нескольких тактов до сотни), определяемые микрокодом устройства управления. Для высокопроизводительных суперскалярных процессоров свойственны глубокий анализ программы, внеочередное исполнение операций.

- Процессор с упрощённым набором инструкций , англ. RISC - Reduced Instruction Set Computer . В этой архитектуре значительно более простое устройство управления. Большинство инструкций RISC-процессора содержат одинаковое малое число операций (1, иногда 2-3), а сами командные слова в подавляющем числе случаев имеют одинаковую ширину (PowerPC, ARM), хотя бывают исключения (Coldfire). У суперскалярных процессоров - простейшая группировка инструкций без изменения порядка исполнения.

- Процессор с явным параллелизмом , англ. EPIC - Explicitly Parallel Instruction Computer (-ing , термин ® Intel, HP). Отличается от прочих прежде всего тем, что последовательность и параллельность исполнения операций и их распределение по функциональным устройствам явно определены программой. Такие процессоры могут обладать большим количеством функциональных устройств без особого усложнения устройства управления и потерь эффективности. Обычно такие процессоры используют широкое командное слово, состоящее из нескольких слогов, определяющих поведение каждого функционального устройства в течение такта.

- Процессор с минимальным набором инструкций , англ. MISC - Minimal Instruction Set Computer . Эта архитектура определяется прежде всего сверхмалым количеством инструкций (несколько десятков), и почти все они нуль-операндные. Такой подход даёт возможность очень плотно упаковать код, выделив под одну инструкцию от 5 до 8 бит. Промежуточные данные в таком процессоре обычно хранятся на внутреннем стеке, и операции производятся над значениям на вершине стека. Эта архитектура тесно связана с идеологией программирования на языке Forth и обычно используется для исполнения программ, написанных на этом языке.

- Процессор с изменяемым набором инструкций , англ. WISC - Writable Instruction Set Computer . Архитектура, позволяющая перепрограммировать себя, изменяя набор инструкций, подстраивая его под решаемую задачу.

- Транспорт-управляемый процессор , англ. TTA - Transort Triggered Architecture . Архитектура изначально ответвилась от EPIC, но принципиально отличающаяся от остальных тем, что инструкции такого процессора кодируют функциональные операции, а так называемые транспорты - пересылки данных между функциональными устройствами и памятью в произвольном порядке.

По способу хранения программ выделяется две архитектуры:

- Архитектура фон Неймана . В процессорах этой архитектуры используется одна шина и одно устройство ввода-вывода для обращения к программе и данным.

- Гарвардская архитектура . В процессорах этой архитектуры для выборки программ и обмена данным существуют отдельные шины и устройства ввода-вывода. Во встроенных микропроцессорах, микроконтроллерах и ПЦОС это также определяет существование двух независимых запоминающих устройств для хранения программ и данных. В центральных процессорах это определяет существование отдельного кэша инструкций и данных. За кэшем шины могут быть объединены в одну посредством мультиплексирования.

По организации регистрового файла ФУ можно выделить следующие типы процессоров.

- Регистровая архитектура - характеризуется свободным доступом к регистрам для выборки всех аргументов и записи результата. Элементарны арифметико-логические операции в таких процессорах кодируются в двух-, или трёхоперандные инструкции (регистр+регистр→регистр, иногда регистр результата совпадает с источником одного из агрументов).

- Аккумуляторная архитектура - из регистров выделяется один из несколько регистров-аккумуляторов. Регистр-аккумулятор является источником одного из аргументов и приёмником результата вычислений. Операции кодируются как правило в однооперандные инструкции (аккумулятор+операнд→аккумулятор). Такая архитектура характерная для многих CISC-процессоров (напр. Z80).

- Стековая архитектура - определяется организацией регистрового файла в виде стека, и косвенной адресацией регистров через указатель стека, который определяет положение вершины стека, операции производятся над значениями на вершине стека и результат кладётся также на вершину. Арифметические операции кодируются в нуль-операндные инструкции. Стековая архитектура является неотъемлемой частью MISC-процессоров.

1.6.1 Основные понятия

Развитие технологии обеспечивает возможность создания на кристалле все большего количества активных компонентов - транзисторов, которые могут быть использованы для реализации новых архитектурных и структурных решений, обеспечивающих повышение производительности и расширение функциональных возможностей микропроцессоров

Микропроцессорная техника включает технические и программные средства, используемые для построения различных микропроцессорных систем, устройств и персональных микроЭВМ.

Микропроцессор (МП) – программно-управляемое устройство, осуществляющее процесс цифровой обработки информации и управления им и построенное, как правило, на одной БИС.

Микропроцессорная система (МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, главным образом, микропроцессорных: микропроцессора и/или микроконтроллера.

Термин «микроконтроллер» (МК) вытеснил из употребления ранее использовавшийся термин «однокристальная микроЭВМ». Первый же патент на однокристальную микро-ЭВМ был выдан в 1971 году М. Кочрену и Г. Буну. Именно они предложили на одном кристалле разместить не только микропроцессор, но и память, устройства ввода-вывода. С появлением однокристальных микроЭВМ связывают начало эры компьютерной автоматизации в области управления. По-видимому, это обстоятельство и определило термин «микроконтроллер» (control - управление).

Однако впоследствии расширение сферы использования МК повлекло за собой развитие их архитектуры за счет размещения на кристалле устройств (модулей), отражающих своими функциональными возможностями специфику решаемых задач. Такие дополнительные устройства стали называться периферийными. Поэтому неслучайно в последнее время введен еще один термин - «интегрированный процессор» (ИП) , который определяет новый класс функционально-емких однокристальных устройств с другим составом модулей. По количеству и составу периферийных устройств ИП уступают МК и занимают промежуточное положение между МП и МК. По этой же причине появились не только семейства МК, которые объединяют родственные МК (с одинаковой системой команд, разрядностью), но и стали выделяться подвиды МК: коммуникационные, для управления и т. д.

Микроконтроллер (МК) – однокристальная ЭВМ или управляющий микропроцессор.

МП в настоящее время преимущественно используются для производства персональных ЭВМ, а МК и ИП являются основой создания различных встраиваемых систем, телекоммуникационного и портативного оборудования и т. д.

Архитектурой процессора называется комплекс его аппаратных и программныхсредств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти и т.д.

Архитектура тесно связана соструктурой , которая предусматривает наличие компонентов для реализации функций процессора.

1.6.2 Варианты архитектур микропроцессоров

В зависимости от набора выполняемых команд и способов адресации

CISC ( Complex Instruction Set Computer ) – архитектура реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации.

Например, микропроцессоры семейства Pentium. Они выполняют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации).

Большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Однако при этом существенноусложняется структура микропроцессора, особенно его устройства управления, что приводит к увеличению размеров и стоимости кристалла, снижению производительности. В то же время многие команды и способы адресации используются достаточно редко. Поэтому, начиная с 1980-х годов, интенсивное развитие получила архитектура процессоров с сокращенным набором команд ( RISC -процессоры).

RISC ( Reduced Instruction Set Computer ) – архитектура отличается использованием ограниченного набора команд фиксированного формата и сокращенного числа способов адресации. В результате существенно упрощается структура микропроцессора, сокращаются его размеры и стоимость, значительно повышается производительность.

Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. При этом для сокращения количества обращений к памяти RISC-процессоры имеют увеличенный объем внутреннего регистрового запоминающего устройства – от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначения обычно составляет 8-16.Обращение к памяти в RISC-процессорах используется только в операциях загрузки данных в РЭУ или пересылки результатов из РЭУ в память. При этом используется небольшое число наиболее простых способов адресации: косвенно-регистровая, индексная и некоторые другие.

Достоинства RISC-архитектуры привели к тому, что во многих современных CISC-процессорах используется RISC-ядро, выполняющее обработку данных. При этом поступающие сложные и разноформатные команды предварительно преобразуются в последовательность простых RISC-операций, быстро выполняемых этим процессорным ядром.

Таким образом работают, например, последние модели микропроцессоров Pentium и К7, которые по внешним показателям относятся к CISC-процессорам. Использование RISC-архитектуры является характерной чертой многих современных микропроцессоров.

VLIW ( Very Large Instruction Word ) – особенностью архитектуры является использование очень длинных команд(до 128 бит и более), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций параллельно в различных операционных устройствах, входящих в структуру микропроцессора.

Архитектура появилась относительно недавно - в 1990-х годах.

В зависимостиот используемого варианта реализации памяти и организации выборки команд и данных в современных микропроцессорах реализуются следующие варианты архитектур:

Принстонская архитектура , которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ и данных. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные.

Достоинства архитектуры:

а) Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных в зависимости от решаемых задач. Этим обеспечивается возможность эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения микропроцессора;

б) использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность.

Основным недостатком архитектуры является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится «узким местом» (bottleneck - «бутылочное горло»), которое ограничивает производительность цифровой системы.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды.

Достоинством архитектуры является более высокая производительность, чем при использовании Принстонской архитектуры, благодаря разделению потоков команд и данных и совмещению операций их выборки.

Недостатки архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи.

Поэтому приходится использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки.

Гар вардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципыПринстонской архитектуры .

Типовая структура микропроцессорной системы

Большинство микропроцессорных систем имеет магистрально-модульную структуру, в которой отдельные устройства (модули), входящие в состав системы, обмениваются информацией по общей системной шине–магистрали (рисунок 1.7).

Основным модулем системы является микропроцессор, в состав которого входят

устрой ство управления (УУ) ,

операционное устройство ,

регистровое запоминающее уст ройство (РЗУ) –внутренняя память, реализованная в виде набора регистров.

Опера тивное запоминающее устройство (ОЗУ) служит для хранения выполняемой программы (или ее фрагментов) и данных, подлежащих обработке. В простейших микропроцессорных системах объем ОЗУ составляет десятки и сотни байт, а современных персональных компьютерах, серверах и рабочих станциях он достигает сотен Мбайт и более. Так как обращение к ОЗУ по системной шине требует значительных затрат времени,в большинстве современных высокопроизводительных микропроцессоров дополнительно вводитсябыстродействующая промежуточная память (кэш-память) ограниченного объема (от нескольких Кбайт до сотен Кбайт).

Постоянное запоминающее устройство (ПЗУ) служит для хранения констант и стандартных (неизменяемых) программ. В ПЗУ обычно записываются программы начальной инициализации (загрузки) систем, тестовые и диагностические программы и другое служебное программное обеспечение, которое не меняется в процессе эксплуатации систем. В микропроцессорных системах, управляющих определенными объектами с использованием фиксированных или редко изменяемых программ, для их хранения также обычно используется ПЗУ (память ROM – Read-Only Memory) или репрограммируемое ПЗУ (память EEPROM – Electrically Erased Programmable Read-Only Memory или флэш-память).

Интер фейсные устройства (ИУ) служат для подключения к шине остальных устройств, которые являются внешними по отношению к системе. ИУ реализуют определенные протоколы параллельного или последовательного обмена. Внешними устройствами могут быть клавиатура, монитор, внешние запоминающие устройства (ВЗУ), использующие гибкие или жесткие магнитные диски, оптические диски (CD-ROM), магнитные ленты и другие виды носителей информации, датчики и преобразователи информации (аналого-цифровые или цифроаналоговые), разнообразные исполнительные устройства (индикаторы, принтеры, электродвигатели, реле и другие).

Для реализации различных режимов работы к системе могут подключаться дополнительные устройства – контроллеры прерываний, прямого доступа к памяти и другие, реализующие необходимые специальные функции управления.

Данная структура соответствует архитектуре Фон-Неймана, предложенной этим ученым в 1940-х годах для реализации первых моделей цифровых ЭВМ.

УУ – устройство управления

ОУ – операционное устройство

РЗУ– регистровое запоминающее устройство

ОЗУ – оперативное запоминающее устройство

ПЗУ – постоянное запоминающее устройство

ИУ – интерфейсное устройство

Рисунок 1.7 – Типовая структура микропроцессорной системы

Системная шина содержит несколько десятков (в сложных системах более 100) проводников, которые в соответствии с их функциональным назначением подразделяются на отдельные шины:

шина адреса А , служит для передачи адреса, который формируется микропроцессором и позволяет выбрать необходимую ячейку памяти ОЗУ (ПЗУ) или требуемое ИУ при обращении к внешнему устройству;

шина данных D , служит для выборки команд, поступающих из ОЗУ или ПЗУ в УУ микропроцессора, и для пересылки обрабатываемых данных (операндов) между микропроцессором и ОЗУ или ИУ (внешним устройством);

шина управления С , служит для передачи разнообразных управляющих сигналов, определяющих режимы работы памяти (запись или считывание), интерфейсных устройств (ввод или вывод информации) и микропроцессора (запуск, запросы внешних устройств на обслуживание, информация о текущем режиме работы) и другие сигналы.

Введение

Введение

Микропроцессоры и микроконтроллеры являются одной из наиболее динамично развивающихся областей современной электронной техники. Впервые появившись в 1971 году, эти электронные приборы быстро прошли путь от простейших устройств, выполняющих несложные вычисления, до современных высокопроизводительных процессоров, реализующих сотни миллионов операций в секунду. Еще более впечатляющим является лавинообразное расширение их областей применения. В настоящее время на производстве и в быту нас окружают десятки микропроцессоров и микроконтроллеров, встроенных в аппаратуру различного назначения. Это не только персональные компьютеры, которые стали обязательным атрибутом, как домашнего интерьера, так и рабочего места специалистов во многих сферах производства и обслуживания. Это и современная бытовая техника, средства проведения досуга, автомобильная электроника и медицинская аппаратура, средства связи, разноообразные приборы и системы, используемые в производственном оборудовании, и многое другое.

Знание основ микропроцессорной техники является необходимым для многих специалистов, как разрабатывающих новые виды устройств на базе современных микропроцессоров и микроконтроллеров, так и использующих в своей профессиональной деятельности аппаратуру, реализованную на их основе. Данное учебное пособие имеет целью помочь освоению этой техники широкому кругу специалистов, выпускаемых учебными заведениями для различных отраслей народного хозяйства.

Современная электронная цифровая вычислительная техника широко применяется в народном хозяйстве. В настоящее время создано четыре поколения ЭВМ с улучшающимися технико-экономическими показателями, что способствует дальнейшему расширению сферы применения ЭВМ и их эффективности.

Микроконтроллеры являются наиболее массовым представителем микропроцессорной техники. Интегрируя на одном кристалле высоко производительный процессор, память и набор периферийных устройств, микроконтроллеры позволяют с минимальными затратами реализовать широкую номенклатуру систем управления различными объектами и процессами. Использование микроконтроллеров в системах управления и обработки информации обеспечивает исключительно высокие показатели эффективности при достаточно низкой стоимости. Микроконтроллерам практически нет альтернативы, когда нужно создать качественные и дешевые системы. Иногда система может состоять только из одного микроконтроллера. Исключение составляет применение программируемых логических интегральных схем (ПЛИС) в области обработки сигналов в том случае, когда требуется параллельная обработка большого потока входных данных.

микропроцессор микроконтроллер архитектура вычислительный

1. Микропроцессоры, функциональные возможности и архитектурные решения

Развитие технологии обеспечивает возможность создания на кристалле все большего количества активных компонентов - транзисторов, которые могут быть использованы для реализации новых архитектурных и структурных решений, обеспечивающих повышение производительности и расширение функциональных возможностей микропроцессоров. Кратко рассмотрим основные из этих решений.

Архитектурой процессора называется комплекс его аппаратных и программных средств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти, виды и способы обработки прерываний. Например, все модификации процессоров Pentium, Celeron, i486 и i386 имеют архитектуру IA-32 (Intel Architecture - 32 bit), которая характеризуется стандартным набором регистров, предоставляемых пользователю, общей системой основных команд и способов организации и адресации памяти, одинаковой реализацией защиты памяти и обслуживания прерываний.

При описании архитектуры и функционирования процессора обычно используется его представление в виде совокупности программно-доступных регистров, образующих регистровую или программную модель. В этих регистрах содержатся обрабатываемые данные (операнды) и управляющая информация. Соответственно, в регистровую модель входит группа регистров общего назначения, служащих для хранения операндов, и группа служебных регистров, обеспечивающих управление выполнением программы и режимом работы процессора, организацию обращения к памяти (защита памяти, сегментная и страничная организация и др.).

Регистры общего назначения образуют РЗУ - внутреннюю регистровую память процессора (см. раздел 1.3). Состав и количество служебных регистров определяется архитектурой микропроцессора. Обычно в их состав входят:

программный счетчик PC (или CS + IP в архитектуре микропроцессоров Intel),

регистр состояния SR (или EFLAGS),

регистры управления режимом работы процессора CR (Control Register),

регистры, реализующие сегментную и страничную организацию памяти,

регистры, обеспечивающие отладку программ и тестирование процессора.

Кроме того, различные модели микропроцессоров содержат ряд других специализированных регистров.

Функционирование процессора представляется в виде реализации регистровых пересылок - процедур проверки и изменения состояния этих регистров путем чтения-записи их содержимого. В результате таких пересылок обеспечивается адресация и выбор команд и операндов, хранение и пересылка результатов, изменение последовательности команд и режимов функционирования процессора в соответствии с поступлением нового содержимого в служебные регистры, а также все другие процедуры, реализующие процесс обработки информации согласно заданным условиям.

В ряде процессоров выделяются регистры, которые используются при выполнении прикладных программ и доступны каждому пользователю, и регистры, которые управляют режимом работы всей системы и доступны только для привилегированных программ, входящих в состав операционной системы (супервизора). Соответственно, такие процессоры представляются в виде регистровой модели пользователя, в которую входят регистры, используемые при выполнении прикладных программ, или регистровой модели супервизора, которая содержит весь набор программно-доступных регистров процессора, используемых операционной системой.

Структура микропроцессора определяет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле. В эту структуру входят:

центральный процессор (процессорное ядро), состоящее из устройства управления (УУ), одного или нескольких операционных устройств (ОУ),

внутренняя память (РЗУ, кэш-память, в микроконтроллерах - блоки оперативной и постоянной памяти),

интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода-вывода,

периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры),

различные вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других).

Состав устройств и блоков, входящих в структуру микропроцессора, и реализуемые механизмы их взаимодействия определяются функциональным назначением и областью применения микропроцессора.

Архитектура и структура микропроцессора тесно взаимосвязаны. Реализация тех или иных архитектурных особенностей требует введения в структуру микропроцессора необходимых аппаратных средств (устройств и блоков) и обеспечения соответствующих механизмов их совместного функционирования.

В современных микропроцессорах реализуются следующие варианты архитектур.(Complex Instruction Set Computer) - архитектура реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Эта классическая архитектура процессоров, которая начала свое развитие в 40-х годах прошлого века с появлением первых компьютеров. Типичным примером CISC-процессоров являются микропроцессоры семейства Pentium. Они выполняют более 300 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. Такое большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Однако при этом существенно усложняется структура микропроцессора, особенно его устройства управления, что приводит к увеличению размеров и стоимости кристалла, снижению производительности. В то же время многие команды и способы адресации используются достаточно редко. Поэтому, начиная с 80-х годов прошлого века, интенсивное развитие получила архитектура процессоров с сокращенным набором команд (RISC-процессоры).(Reduced Instruction Set Computer) - архитектура отличается использованием ограниченного набора команд фиксированного формата. Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 2 или 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. При этом для сокращения количества обращений к памяти RISC-процессоры имеют увеличенный объем внутреннего РЗУ - от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначения обычно составляет 8-16.

Обращение к памяти в RISC-процессорах используется только в операциях загрузки данных в РЗУ или пересылки результатов из РЗУ в память. При этом используется небольшое число наиболее простых способов адресации: косвенно-регистровая, индексная и некоторые другие. В результате существенно упрощается структура микропроцессора, сокращаются его размеры и стоимость, значительно повышается производительность.

Указанные достоинства RISC-архитектуры привели к тому, что во многих современных CISC-процессорах используется RISC-ядро, выполняющее обработку данных. При этом поступающие сложные и разноформатные команды предварительно преобразуются в последовательность простых RISC-операций, быстро выполняемых этим процессорным ядром. Таким образом, работают, например, последние модели микропроцессоров Pentium и K7, которые по внешним показателям относятся к CISC-процессорам. Использование RISC-архитектуры является характерной чертой многих современных микропроцессоров.(Very Large Instruction Word) - архитектура появилась относительно недавно - в 90-х годах. Ее особенностью является использование очень длинных команд (до 128 бит), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций, которые могут производиться параллельно в различных операционных устройствах, входящих в структуру микропроцессора. При трансляции программ, написанных на языке высокого уровня, соответствующий компилятор производит формирование "длинных" VLIW-команд, каждая из которых обеспечивает реализацию процессором целой процедуры или группы операций. Данная архитектура реализована в некоторых типах современных микропроцессоров (PA8500 компании Hewlett-Packard, Itanium - совместная разработка Intel и Hewlett-Packard, некоторые типы DSP - цифровых процессоров сигналов) и является весьма перспективной для создания нового поколения сверхвысокопроизводительных процессоров.

Кроме набора выполняемых команд и способов адресации важной архитектурной особенностью микропроцессоров является используемый вариант реализации памяти и организация выборки команд и данных. По этим признакам различаются процессоры с Принстонской и Гарвардской архитектурой. Эти архитектурные варианты были предложены в конце 40-х годов специалистами, соответственно, Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров.

Принстонская архитектура, которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Структура и функционирование цифровой системы с Принстонской архитектурой описаны в разделе 1. Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения микропроцессора. Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Поэтому Принстонская архитектура в течение долгого времени доминировала в вычислительной технике.

Однако ей присущи и существенные недостатки. Основным из них является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится "узким местом" (bottle-neck - "бутылочное горло"), которое ограничивает производительность цифровой системы. Постоянно возрастающие требования к производительности микропроцессорных систем вызвали в последние годы все более широкое применение Гарвардской архитектуры при создании многих типов современных микропроцессоров.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры.

Недостатки Гарвардской архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходиться использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки, поэтому Гарвардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципы Принстонской архитектуры.

Гарвардская архитектура получила также широкое применение в микроконтроллерах - специализированных микропроцессорах для управления различными объектами, рабочая программа которых обычно хранится в отдельном ПЗУ.

В современных микропроцессорах используются разнообразные способы предсказания ветвлений. Наиболее простой способ состоит в том, что процессор фиксирует результат выполнения предыдущих команд ветвления по данному адресу, и считает, что следующая команда с обращением по этому адресу даст аналогичный результат. Данный способ предсказания предполагает более высокую вероятность повторного обращения к определенной команде, задаваемой данным условием ветвления. Для реализации этого способа предсказания ветвления используется специальная память BTB (Branch Target Buffer), где хранятся адреса ранее выполненных условных переходов. При поступлении аналогичной команды ветвления предсказывается переход к ветви, которая была выбрана в предыдущем случае, и производится загрузка в конвейер команд из соответствующей ветви. При правильном предсказании не требуется перезагрузка конвейера, и эффективность его использования не снижается. Эффективность такого способа предсказания зависит от емкости BTB и оказывается достаточно высокой: вероятность правильного предсказания составляет 80% и более. Повышение точности предсказания достигается при использовании более сложных способов, когда хранится и анализируется предистория переходов - результаты нескольких предыдущих команд ветвления по данному адресу. В этом случае возможно определение чаще всего реализуемого направления ветвления, а также выявление чередующихся переходов. Реализация таких алгоритмов требует использования более сложных блоков предсказания, но при этом вероятность правильного предсказания повышается до 90-95 %.

Возможность повышения производительности процессора достигается также при введении в структуру процессора нескольких параллельно включенных операционных устройств, обеспечивающих одновременное выполнение нескольких операций. Такая структура процессора называется суперскалярной. В этих процессорах реализуется параллельная работа нескольких исполнительных конвейеров, в каждый из которых поступает для выполнения одна из выбранных и декодированных команд. В идеальном случае число одновременно выполняемых команд равно числу операционных устройств, включенных в исполнительные конвейеры. Однако при выполнении реальных программ трудно обеспечить полную загрузку всех исполнительных конвейеров, поэтому на практике эффективность использования суперскалярной структуры оказывается несколько ниже. Современные суперскалярные процессоры содержат до 4 до 10 различных операционных устройств, параллельная работа которых обеспечивает выполнение за один такт в среднем от 2 до 6 команд.

Эффективная одновременная работа нескольких исполнительных конвейеров обеспечивается путем предварительной выборки-декодирования ряда команд и выделения из них группы команд, которые могут выполняться одновременно. В современных суперскалярных процессорах производится выборка нескольких десятков команд, которые декодируются, анализируются и группируются для параллельной загрузки в исполнительные конвейеры. Обычно в процессорах имеется несколько устройств для выполнения целочисленных операций, одно или несколько устройств для обработки чисел с плавающей точкой, отдельные устройства для обработки специальных форматов видео - и аудиоданных. Параллельно работают также устройства формирования адресов и выборки операндов для загружаемых команд. При этом обычно реализуется предварительная (спекулятивная) выборка операндов, чтобы для поступающих на исполнение команд уже были готовы операнды, которые записываются в специальные регистры. Чтобы обеспечить наиболее полную загрузку исполнительных конвейеров, в процессе анализа и группировки декодированных команд возможно изменение порядка их следования. В результате команды выполняются не в порядке их выборки из памяти, а по мере готовности необходимых операндов и исполнительных устройств. Таким образом, позже поступившие команды могут быть выполнены до ранее выбранных. Чтобы запись в память результатов происходила в соответствии с исходной последовательностью поступления команд программы, на выходе данных включается специальная буферная память, восстанавливающая порядок выдачи результатов согласно выполняемой программе.

Одновременное параллельное выполнение команд может оказаться невозможным, если они обращаются к одному регистру. При ограниченной емкости РЗУ процессора такие случаи могут возникать достаточно часто, что снижает эффективность работы исполнительных конвейеров. Поэтому в ряде процессоров вводятся специальные регистровые блоки, дублирующие РЗУ. При поступлении команд, которые обращаются к одинаковым регистрам РЗУ, производится их переадресация к дублирующим регистровым блокам - "переименование" регистров. В результате обеспечивается возможность одновременного выполнения таких команд, что позволяет реализовать более эффективную параллельную работу исполнительных конвейеров.

Рис. 1. Классификация современных микропроцессоров по функциональному признаку.

Хотя микропроцессор является универсальным средством для цифровой обработки информации, однако отдельные области применения требуют реализации определенных специфических вариантов их структуры и архитектуры. Поэтому по функциональному признаку выделяются два класса: микропроцессоры общего назначения и специализированные микропроцессоры (рисунок 1). Среди специализированных микропроцессоров наиболее широкое распространение получили микроконтроллеры, предназначенные для выполнения функций управления различными объектами, и цифровые процессоры сигналов (DSP - Digital Signal Processor), которые ориентированы на реализацию процедур, обеспечивающих необходимое преобразование аналоговых сигналов, представленных в цифровой форме.

Микропроцессоры общего назначения предназначены для решения широкого круга задач обработки разнообразной информации. Их основной областью использования являются персональные компьютеры, рабочие станции, серверы и другие цифровые системы массового применения. К этому классу относятся CISC-процессоры Pentium компании Intel, K7 компании Advanced MicroDevices (AMD), 680x0 компании Motorola, RISC-процессоры PowerPC, выпускаемые компаниями Motorola и IBM, SPARC компании Sun Microsystems и ряд других изделий различных производителей.

Расширение области применения таких микропроцессоров достигается, главным образом, путем роста производительности, благодаря чему увеличивается круг задач, который можно решать с их использованием. Поэтому повышение производительности является магистральным направлением развития этого класса микропроцессоров. Обычно это 32-разрядные микропроцессоры (некоторые микропроцессоры этого класса имеют 64-разрядную или 128-разрядную структуру), которые изготавливаются по самой современной промышленной технологии, обеспечивающей максимальную частоту функционирования.

Ряд наиболее популярных микропроцессоров этого класса (Pentium, AMD K7 и некоторые другие) следует отнести к CISC-процессорам, так как они выполняют большой набор разноформатных команд с использованием многочисленных способов адресации. Однако в их внутренней структуре содержится RISC-процессор, который выполняет поступившие команды после их преобразования в последовательность простых RISC-операций. Ряд других микропроцессоров этого класса непосредственно реализует RISC-архитектуру. Поэтому можно считать, что использование RISC-архитектуры характерно для большинства этих микропроцессоров.

В ряде последних разработок (Itanium, PA8500) некоторых ведущих производителей успешно применяются принципы VLIW-архитектуры, которая может составить конкуренцию RISC-архитектуре в соревновании за достижение наивысшей производительности.

Практически все современные микропроцессоры этого класса используют Гарвардскую внутреннюю архитектуру, где разделение потоков команд и данных реализуется с помощью отдельных блоков кэш-памяти (рис.1). В большинстве случаев они имеют суперскалярную структуру с несколькими исполнительными конвейерами (до 10 в современных моделях), которые содержат до 20 ступеней.

Благодаря своей универсальности микропроцессоры общего назначения используются также в специализированых системах, где требуется высокая производительность. На их основе реализуются одноплатные компьютеры и промышленные компьютеры, которые применяются в системах управления различными объектами. Одноплатные (встраиваемые) компьютеры содержат на плате необходимые дополнительные микросхемы, обеспечивающие их специализированное применение, и предназначены для встраивания в аппаратуру различного назначения. Промышленные компьютеры размещаются в корпусах специальной конструкции, обеспечивающих их надежную работу в жестких производственных условиях. Обычно такие компьютеры работают без стандартных периферийных устройств (монитор, клавиатура, "мышь) или используют специальные варианты этих устройств, модифицированные с учетом специфических условий применения.

2. Микроконтроллеры, функциональные возможности и архитектурные решения

Микроконтроллеры являются наиболее массовым представителем микропроцессорной техники. Интегрируя на одном кристалле высокопроизводительный процессор, память и набор периферийных устройств, микроконтроллеры позволяют с минимальными затратами реализовать широкую номенклатуру систем управления различными объектами и процессами. Использование микроконтроллеров в системах управления и обработки информации обеспечивает исключительно высокие показатели эффективности при достаточно низкой стоимости. Микроконтроллерам практически нет альтернативы, когда нужно создать качественные и дешевые системы. Иногда система может состоять только из одного микроконтроллера. Исключение составляет применение программируемых логических интегральных схем (ПЛИС) в области обработки сигналов в том случае, когда требуется параллельная обработка большого потока входных данных. Основным классификационным признаком микроконтроллеров является разрядность микропроцессора. Имеются 4-, 8-, 16-, 32-разрядные микроконтроллеры. Разрядность микроконтроллера определяется точностью данных, необходимых для управления объектом. Наиболее массовыми и постоянно расширяющими свои области применения являются 8-разрядные микроконтроллеры, которые дешевле 16 - и 32-разрядных и имеют большую функциональность.

Промышленностью выпускаются очень широкая номенклатура встраиваемых МК. В них все необходимые ресурсы (память, устройства ввода-вывода и т.д.) располагаются на одном кристалле с процессорным ядром. Если подать питание и тактовые импульсы на соответствующие входы МК, то можно сказать, что он как бы "оживет" и с ним можно будет работать. Обычно МК содержат значительное число вспомогательных устройств, благодаря чему обеспечивается их включение в реальную систему с использованием минимального количества дополнительных компонентов. В состав этих МК входят:

Схема начального запуска процессора (Reset);

Генератор тактовых импульсов;

Центральный процессор;

Память программ (E (E) PROM) и программный интерфейс;

Средства ввода/вывода данных;

Таймеры, фиксирующие число командных циклов.

Общая структура МК показана на рисунке 4. Эта структура дает представление о том, как МК связывается с внешним миром.

Рисунок 2 - структура микроконтроллера

Более сложные встраиваемые МК могут дополнительно реализовывать следующие возможности:

Встроенный монитор/отладчик программ;

Внутренние средства программирования памяти программ (ROM);

Обработка прерываний от различных источников;

Аналоговый ввод/вывод;

Последовательный ввод/вывод (синхронный и асинхронный);

Параллельный ввод/вывод (включая интерфейс с компьютером);

Подключение внешней памяти (микропроцессорный режим).

Все эти возможности значительно увеличивают гибкость применения МК и делают более простым процесс разработки систем на и основе.

Некоторые МК (особенно 16 - и 32-разрядные) используют только внешнюю память, которая включает в себя как память программ (ROM), так и некоторый объем памяти данных (RAM), требуемый для данного применения. Они применяются в системах, где требуется большой объем памяти и относительное не большое количество устройств (портов) ввода/вывода. Типичным примером применения такого МК с внешней памятью является котроллер жесткого диска (HDD) с буферной кэш-памятью, который обеспечивает промежуточное хранение и распределение больших объемов данных (порядка нескольких мегабайт). Внешняя память дает возможность такому микроконтроллеру работать с более высокой скоростью, чем встраиваемый МК.

Цифровые сигнальные процессоры (DSP) - относительно новая категория процессоров. Назначение DSP состоит в том, чтобы получать текущие данные от аналоговой системы, обрабатывать данные и формировать соответствующий отклик в реальном масштабе времени. Они обычно входят в состав систем, используясь в качестве устройств управления внешним оборудованием, и не предназначены для автономного применения.

Микроконтроллеры являются специализированными микропроцессорами, которые ориентированы на реализацию устройств управления, встраиваемых в разнообразную аппаратуру. Ввиду огромного количества объектов, управление которыми обеспечивается с помощью микроконтроллеров, годовой объем их выпуска превышает 2 миллиарда экземпляров, на порядок превосходя объем выпуска микропроцессоров общего применения. Весьма широкой является также номенклатура выпускаемых микроконтроллеров, которая содержит несколько тысяч типов.

Характерной особенностью структуры микроконтроллеров является размещение на одном кристалле с центральным процессором внутренней памяти и большого набора периферийных устройств. В состав периферийных устройств обычно входят несколько 8-разрядных параллельных портов ввода-вывода данных (от 1 до 8), один или два последовательных порта, таймерный блок, аналого-цифровой преобразователь. Кроме того, различные типы микроконтроллеров содержат дополнительные специализированные устройства - блок формирования сигналов с широтно-импульсной модуляцией, контроллер жидко-кристаллического дисплея и ряд других. Благодаря использованию внутренней памяти и периферийных устройств реализуемые на базе микроконтроллеров системы управления содержат минимальное количество дополнительных компонентов.

В связи с широким диапазоном решаемых задач управления требования, предъявляемые к производительности процессора, объему внутренней памяти команд и данных, набору необходимых периферийных устройств, оказываются весьма разнообразными. Для удовлетворения запросов потребителей выпускается большая номенклатура микроконтроллеров, которые принято подразделять на 8-, 16 - и 32-разрядные.

Разрядные микроконтроллеры представляют наиболее многочисленную группу этого класса микропроцессоров. Они имеют относительно низкую производительность, которая, однако, вполне достаточна для решения широкого круга задач управления различными объектами. Это простые и дешевые микроконтроллеры, ориентированные на использование в относительно несложных устройствах массового выпуска. Основными областями их применения являются бытовая и измерительная техника, промышленная автоматика, автомобильная электроника, теле-, видео - и аудиоаппаратура, средства связи, медицинские приборы.

Для этих микроконтроллеров характерна реализация Гарвардской архитектуры, где используется отдельная память для хранения программ и данных. Для хранения программ в различных типах микроконтроллеров применяется либо масочно-программируемое ПЗУ (ROM), либо однократно-программируемое ПЗУ (PROM), либо электрически репрограммируемое ПЗУ (EPROM, EEPROM или Flash). Внутренняя память программ обычно имеет объем от нескольких единиц до десятков Кбайт. Для хранения данных используется регистровый блок, организованный в виде нескольких регистровых банков, или внутреннего ОЗУ. Объем внутренней памяти данных составляет от нескольких десятков байт до нескольких Кбайт. Ряд микроконтроллеров этой группы позволяет, в случае необходимости, дополнительно подключать внешнюю память команд и данных, объемом до 64 - 256 Кбайт.

Микроконтроллеры этой группы обычно выполняют относительно небольшой набор команд (50-100), использующих наиболее простые способы адресации. В ряде последних моделей этих микроконтроллеров реализованы принципы RISC-архитектуры, что позволяет существенно повысить их производительность. В результате, такие RISC-микроконтроллеры обеспечивают выполнение большинства команд за один такт машинного времени.

Разрядные микроконтроллеры во многих случаях являются усовершенствованной модификацией своих 8-разрядных прототипов. Они характеризуются не только увеличенной разрядностью обрабатываемых данных, но и расширенной системой команд и способов адресации, увеличенным набором регистров и объемом адресуемой памяти, а также рядом других дополнительных возможностей, использование которых позволяет повысить производительность и обеспечить новые области применения. Обычно эти микроконтроллеры позволяют расширить объем памяти программ и данных до нескольких Мбайт путем подключения внешних микросхем памяти. Во многих случаях реализуется их программная совместимость с младшими 8-разрядными моделями. Основная сфера применения таких микроконтроллеров - сложная промышленная автоматика, телекоммуникационная аппаратура, медицинская и измерительная техника.

Разрядные микроконтроллеры содержат высокопроизводительный процессор, соответствующий по своим возможностям младшим моделям микропроцессоров общего назначения. В ряде случаев процессор, используемый в этих микроконтроллерах, аналогичен CISC - или RISC-процессорам, которые выпускаются или выпускались ранее в качестве микропроцессоров общего назначения. Например, в 32-разрядных микроконтроллерах компании Intel используется процессор i386, в микроконтроллерах компании Motorola широко применяется процессор 68020, в ряде других микроконтроллеров в качестве процессорного ядра служат RISC-процессоры типа PowerPC. На базе данных процессоров были реализованы различные модели персональных компьютеров. Введение этих процессоров в состав микроконтроллеров позволяет использовать в соответствующих системах управления огромный объем прикладного и системного программного обеспечения, созданный ранее для соответствующих персональных компьютеров.

Кроме 32-разрядного процессора на кристалле микроконтроллера размещается внутренняя память команд емкостью до десятков Кбайт, память данных емкостью до нескольких Кбайт, а также сложно-функциональные периферийные устройства - таймерный процессор, коммуникационный процессор, модуль последовательного обмена и ряд других. Микроконтроллеры работают с внешней памятью объемом до 64 Мбайт и выше. Они находят широкое применение в системах управления сложными объектами промышленной автоматики (двигатели, робототехнические устройства, средства комплексной автоматизации производства), в контрольно-измерительной аппаратуре и телекоммуникационном оборудовании.

Во внутренней структуре этих микроконтроллеров реализуется Принстонская или Гарвардская архитектура. Входящие в их состав процессоры могут иметь CISC - или RISC-архитектуру, а некоторые из них содержат несколько исполнительных конвейеров, образующих суперскалярную структуру.

3. Электронно-вычислительные машины. Классификация ЭВМ

Архитектура ЭВМ - это наиболее общие принципы построения ЭВМ, реализующие программное управление работой и взаимодействием основных ее функциональных узлов.

Под архитектурой ЭВМ принято понимать совокупность общих принципов организации аппаратно-программных средств и основных их характеристик, определяющая функциональные возможности ЭВМ при решении соответствующих типов задач. Архитектура ЭВМ включает в себя как структуру, отражающую состав ПК, так и программно - математическое обеспечение. Структура ЭВМ - совокупность элементов и связей между ними. Основным принципом построения всех современных ЭВМ является программное управление.

Классическая архитектура ЭВМ. Основы учения об архитектуре вычислительных машин были заложены Джон фон Нейманом <#"229" src="doc_zip5.jpg" />

Рисунок 3 - Структура ЭВМ

Классификации ЭВМ. Классификация Флинна. <#"justify">·ОКОД (SISD) (single instruction stream / single data stream) - одиночный поток команд и одиночный поток данных. В таких машинах есть только один поток команд, все команды обрабатываются последовательно друг за другом и каждая команда инициирует одну операцию с одним потоком данных.

·ОКМД (SIMD) (single instruction stream / multiple data stream) - одиночный поток команд и множественный поток данных. В архитектурах подобного рода сохраняется один поток команд, включающий, в отличие от предыдущего класса, векторные команды. Это позволяет выполнять одну арифметическую операцию сразу над многими данными - элементами вектора.

·МКОД (MISD) (multiple instruction stream / single data stream) - множественный поток команд и одиночный поток данных. Определение подразумевает наличие в архитектуре многих процессоров, обрабатывающих один и тот же поток данных. Однако ни Флинн, ни другие специалисты в области архитектуры компьютеров до сих пор не смогли представить убедительный пример реально существующей вычислительной системы, построенной на данном принципе.

·МКМД (MIMD) (multiple instruction stream / multiple data stream) - множественный поток команд и множественный поток данных. Этот класс предполагает, что в вычислительной системе есть несколько устройств обработки команд, объединенных в единый комплекс и работающих каждое со своим потоком команд и данных.

Архитектура ОКОД охватывает все однопроцессорные и одномашинные варианты систем, т.е. с одним вычислителем. Все ЭВМ классической структуры попадают в этот класс. Здесь параллелизм вычислений обеспечивается путем совмещения выполнения операций отдельными блоками АЛУ, а также параллельной работой устройств ввода-вывода информации и процессора. Закономерности организации вычислительного процесса в этих структурах достаточно хорошо изучены.

Архитектура ОКМД предполагает создание структур векторной или матричной обработки. Системы этого типа обычно строятся как однородные, т.е. процессорные элементы, входящие в систему, идентичны, и все они управляются одной и той же последовательностью команд. Однако каждый процессор обрабатывает свой поток данных. Под эту схему хорошо подходят задачи обработки матриц или векторов (массивов), задачи решения систем линейных и нелинейных, алгебраических и дифференциальных уравнений, задачи теории поля и др. В структурах данной архитектуры желательно обеспечивать соединения между процессорами, соответствующие реализуемым математическим зависимостям. Как правило, эти связи напоминают матрицу, в которой каждый процессорный элемент связан с соседними.

По данной схеме строились системы: первая суперЭВМ - ILLIAC-IV, отечественные параллельные системы - ПС-2000, ПС-3000. Идея векторной обработки широко использовалась в таких известных суперЭВМ, как Cyber-205 и Gray-I, II, III. Узким местом подобных систем является необходимость изменения коммутации между процессорами, когда связь между ними отличается от матричной. Кроме того, задачи, допускающие широкий матричный параллелизм, составляют достаточно узкий класс задач. Структуры ВС этого типа, по существу, являются структурами специализированных суперЭВМ.

Третий тип архитектуры МКОД предполагает построение своеобразного процессорного конвейера, в котором результаты обработки передаются от одного процессора к другому по цепочке. Выгоды такого вида обработки понятны. Прототипом таких вычислений может служить схема любого производственного конвейера. В современных ЭВМ по этому принципу реализована схема совмещения операций, в которой параллельно работают различные функциональные блоки, и каждый из них делает свою часть в общем цикле обработки команды.

В ВС этого типа конвейер должны образовывать группы процессоров. Однако при переходе на системный уровень очень трудно выявить подобный регулярный характер в универсальных вычислениях. Кроме того, на практике нельзя обеспечить и "большую длину" такого конвейера, при которой достигается наивысший эффект. Вместе с тем конвейерная схема нашла применение в так называемых скалярных процессорах суперЭВМ, в которых они применяются как специальные процессоры для поддержки векторной обработки.

Архитектура МКМД предполагает, что все процессоры системы работают по своим программам с собственным потоком команд. В простейшем случае они могут быть автономны и независимы. Такая схема использования ВС часто применяется на многих крупных вычислительных центрах для увеличения пропускной способности центра. Большой интерес представляет возможность согласованной работы ЭВМ (процессоров), когда каждый элемент делает часть общей задачи. Общая теоретическая база такого вида работ практически отсутствует. Но можно привести примеры большой эффективности этой модели вычислений. Подобные системы могут быть многомашинными и многопроцессорными. Например, отечественный проект машины динамической архитектуры (МДА) - ЕС-2704, ЕС-2727 позволял одновременно использовать сотни процессоров.

Архитектура ЭВМ включает в себя как структуру, отражающую состав ПК, так и программно - математическое обеспечение. Структура ЭВМ - совокупность элементов и связей между ними. Основным принципом построения всех современных ЭВМ является программное управление. Основы учения об архитектуре вычислительных машин были заложены Джон фон Нейманом. Совокупность этих принципов породила классическую (фон-неймановскую) архитектуру ЭВМ.